VLSI :mealy sequence detector verilog code and test bench for 1010 and verilog programming

ฝัง

- เผยแพร่เมื่อ 21 ธ.ค. 2024

- mealy sequence detector verilog code and test bench for 1010

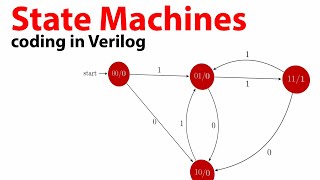

Design of Sequence Detector using FSM in Verilog HDL

In this video Sequence “1010” is detected using MEALY FSM. State diagram, state table are shown

![[VLSI - VERILOG ] verilog code for counter increment by 2 | test bench for counter](/img/n.gif)

There are 2 types of sequence detectors, overlapping and non-overlapping. Here, it is overlapping type. If incase you are looking for a typed code, check this comment: module seq1010(clk, rst, in, out);

input clk,rst,in;

output reg out;

parameter s0 = 2'b00,

s1 = 2'b01,

s2 = 2'b10,

s3 = 2'b11;

reg [1:0] c_state, n_state;

always @(posedge clk or posedge rst)

begin

if(rst) begin

out

Combination circuts you used not blocking statements it's not correct.. please use blocking statments

@@VLSI-learnings Thanks for correcting. made the change. Yet to simulate and check the result.

Please do more videos on verilog hdl your videos are really good

Ok

Do more example bro,,it is helping us lot

Ok

i have exam tmr, this video helped me

Thank you

amazing sir, very clear explanation

Thank you

This is for overlapping case in sequential detector right ?

Yes

@@VLSI-learnings Thank you

i dont understand about "out = 1'b0" 4 turn

Very nice explanation sir..can you tell how to drive data in both clock positive and negative edge

Can we make a sequence detector without using fsm

you have to connect the sequence detector input "in" to 4 serial flops and and take extra four bit input to your design (what sequence you have to detect, give to "1010" to four bit input signal ) and compare with serial flops output with four bit input signal (what you added extra to your design) . you will get the result

suppose

I'm taking input sequence 10101101010111110001010

Then what should I do in case of test bench writing?

I'm mean If I follow your process the testbench will be lengthy, then please teach us another way to write testbench in such case.

use for loop he explained at the end of video.

Bro..! You missed the output instantiation in testbench code

i.e., output as wire

Ok let see

showing Syntax error near "out=1'b0" while simulating on Xilinx ISE software.please help to solve this.

Please check syntax errors in the code... it may be some typo mistakesin code.. you have correct it...

@@VLSI-learnings ok sir

@@mohansardar5247 I got similar error. Then I have updated the code with output reg out. It is working now.

write verilog code for the bidirectional buffer and verify using testbench

very useful, nicely explained

Thank you

will u plz send me the verilog code of sequence detector 0110 using jk flip flop.

i have state diagram and cir cuit diagram but i donnot know how to write the verilog of it.

Why you required this... real time we will use d flop not jk flop

👍👍😍

Nice 👍

Thank you

Thank you

Telugu ga bro?

yes

please dont take your records at airport's plane taking of areas. thanks for information

Ok