How to Write an FSM in SystemVerilog (SystemVerilog Tutorial #1)

ฝัง

- เผยแพร่เมื่อ 28 ส.ค. 2024

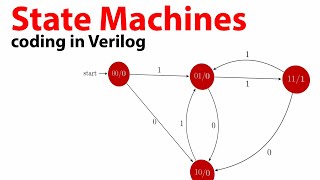

- In this video I show how to write a finite state machine with SystemVerilog in ModelSim.

Video 2 (How to Simulate and Test SystemVerilog with ModelSim):

• How to Simulate and Te...

Video 3 (How to Write a SystemVerilog TestBench):

• How to Write a SystemV...

people need to study this video for how to make youtube tutorials. Straight to the point, no BS, nice pace and a good clear example from the beginning to end. You are rare.

I suspect that the reason YT tutorials (and other content) are often unnecessarily stretched and bloated is because a longer video (longer watchtime) means more ad revenue and general algorithm bonus.

This also applies to websites that do it because of search engine optimization and ads.

In fact, a lot of content on the web these days is designed to steal your time on purpose.

People who make good content like this despite the drawbacks are the real heroes.

Dude you sound exactly like a gaming youtuber I watch. Solarint is his name haha. Great video btw

Thanks for do this video. It is clearly presented and easy to follow.

you saved my life thank you

So clear love it!

Great explanation and easy to understand.

Nice video to learn sir

Good video

Can you please elaborate on the last line i.e. assign Y = (currentState == D | currentState == E); how did you write this line and what did you mean by your explanation as a two and gate connected to a or gate. I'm a beginner and I want to learn Verilog and SystemVerilog, do you have any suggestion for where and how to start to learn it efficiently.

The number left of the "/" in each bubble within the state machine represents the output of the state machine at that state. So for example in state A, the output is 0 (from A/0) and in state D the output is 1 (from D/1). With the last line, I'm saying that the output, Y, should be 1 when it's in the D state OR when it's in the E state -- because those are the only states where the output is 1. For all other states, the output is 0.

Awesome video. Saving me big time :P

Where are you? You are so good. Don't stop...!

Hah, thanks. I have less time since I'm not a student anymore, but you can watch some demos of mine on the Intel FPGA channel (if you're interested!): th-cam.com/video/mQKVQjJnIzA/w-d-xo.html

@@crclayton That is fantastic. Also, Congratulations for working at Intel.

Thanks sir

😍

how can we write the code of dont care situations? Your all situations are 1 or 0, but what about dont cares? Should not we write anything about them?

How would you assign a 2 bit y output based on each state?? I am confused on that. ( EX if state A Y=01, if state B Y=10 etc!!)

fue de gran ayuda. gracias

Thank you so much

Can you please elaborate line 8? I can't understand how you are defining the current and next state.

On line 8 "State" is a type and I'm defining two variables of that type. So "State currentState, nextState;' is like saying "int a, b;"

In the previous statement on line 6, using "typedef" I defined the type "State" as a 3-bit logic signal with the possible values A to E.

Wow that was clear!

Awesome video

is this code can work with xilinix ISE or vivado?

Nice video! Is the code listing available?

i want verilog code for tap fsm and for condition tms==1 for five cycles then the state automatically goes to test logic reset .i want verilog for that condition

it's very good!

I am curious why you used blocking assignments in the combinational case statement instead of non-blocking? I am just getting started in SV, so forgive my ignorance.

You typically always use blocking assignments in combinations blocks, and nonblocking in sequential blocks. In this case I suppose I could have used blocking statements in the combinational logic since it's not sequential logic, but that's generally not how those blocks are written.

@@crclayton Thank you!

Can I get a test bench for this ?

sir can you provide a test bench for this

Aaaand you earned a sub!

Is this one hot encoding?

No. Enum will assign A with 0, B with 1 and so on. So not one hot.

Man good but i don't English )