- 48

- 330 778

Open Logic

Malaysia

เข้าร่วมเมื่อ 22 ส.ค. 2020

DRAM 06 - Storing Data and Memory Interleaving

00:00 Introduction

00:57 Storing data with DDR4

01:15 Storing data with DDR5

01:52 Storing data with LPDDR4 / LPDDR5

02:06 DDR4 x8

02:47 DDR4 x16

03:10 DDR4 x4

03:32 Storing contingent data with incremental addresses

06:18 Storing contingent data with memory / bank interleaving addresses

06:53 Mapping addresses

08:30 Logical address and physical address

00:57 Storing data with DDR4

01:15 Storing data with DDR5

01:52 Storing data with LPDDR4 / LPDDR5

02:06 DDR4 x8

02:47 DDR4 x16

03:10 DDR4 x4

03:32 Storing contingent data with incremental addresses

06:18 Storing contingent data with memory / bank interleaving addresses

06:53 Mapping addresses

08:30 Logical address and physical address

มุมมอง: 193

วีดีโอ

How Bipolar Junction Transistor BJT Works

มุมมอง 5428 วันที่ผ่านมา

00:19 BJT introduction 02:08 Reversed bias junction 02:53 Forward bias junction 03:27 BJT operation with NPN 06:21 BJT operation with PNP 07:17 BJT terminology 08:40 Simple transistor usage example

How PN Junction Works in Semiconductor

มุมมอง 53หลายเดือนก่อน

00:16 PN Junction 00:57 Zero bias 03:31 Forward bias 05:25 Reversed bias 06:56 General usage

Semiconductor: Intrinsic vs P-Type vs N-Type

มุมมอง 44หลายเดือนก่อน

00:20 Intrinsic semiconductor 01:09 P-Type semiconductor 02:16 N-Type semiconductor 03:09 Comparison

How Semiconductor Works

มุมมอง 1363 หลายเดือนก่อน

00:00 Introduction 00:26 Periodic Table / Protons / Electrons / Shell 01:23 Valence electrons 01:55 Covalent bond and examples 02:49 Metallic bond 03:39 Silicon as (intrinsic) semiconductor 05:10 Silicon with doped impurity (extrinsic semiconductor) 05:34 P-type and N-type semiconductor 07:52 Other semiconductor elements / compounds 08:24 Can water conduct electric?

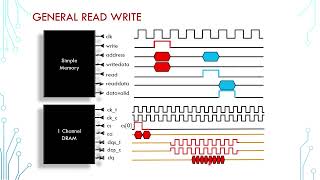

DRAM 05 - General Read and Write Operation on DDR Channel

มุมมอง 2.7K6 หลายเดือนก่อน

00:00 Introduction 00:45 Simple Non DDR Operation 01:53 General DDR Interface 04:04 General DDR Write Operation 05:45 General DDR Read Operation 06:06 Why dqs / data strobe? 07:44 Read / Write latency 08:57 Command to command delay

Writing SV UVM Testbench 04 - Enabling UVM / Hello World in UVM

มุมมอง 3858 หลายเดือนก่อน

00:29 Hello World in SystemVerilog 00:45 Compiling with UVM 02:00 Hello World in UVM 02:47 Exploring simple class with uvm_object

Multiplexer and Demultiplexer

มุมมอง 1918 หลายเดือนก่อน

00:00 Introduction 00:20 AND gate as signal filter 01:19 Controlling multiple signal filters 01:36 Using NOT gate to enable one path but not the other 02:01 Controlling 4 data paths 02:48 Multiplexer 03:03 Demultiplexer 03:26 Example 1 - config status registers 04:21 Example 2 - calibration 05:07 Example 3 - programmable logic

SystemVerilog Tutorial in 5 Minutes 20 - Package

มุมมอง 1.2K9 หลายเดือนก่อน

00:00 Introduction 00:08 Without package 00:54 Introducing package in code 01:48 What package contains 02:39 Multiple packages 03:00 Package importing another package

Writing SV UVM Testbench 03 - Testbench with Classes

มุมมอง 66611 หลายเดือนก่อน

00:18 Test structure with directed test 01:12 Test structure with classes 02:19 Interfaces 03:49 Clock generator 04:48 Design and its instantiation 05:57 Test program and its instantiation 06:10 Test class and its instantiation 07:05 Why the trouble 08:19 Reusability example with test inheritance

DRAM 04 - DIMM, Rank and Channel

มุมมอง 3.3Kปีที่แล้ว

00:00 Introduction 00:20 DRAM structural hierarchy 01:22 DRAM addressing hierarchy 02:16 Memory channel 04:01 Memory ranks on a DIMM 06:12 Memory ranks on a channel / system

SystemVerilog Tutorial in 5 Minutes 16a - Non Blocking Assignment

มุมมอง 2.5Kปีที่แล้ว

00:00 Intro 00:46 Modelling design in structural manner 01:25 Modelling design in behavioral manner 02:55 Non-blocking assignment 03:15 Concurrent behavior with non-blocking assignment 04:11 Blocking and non blocking / module vs program

Writing SV UVM Testbench 02 - Simple Directed Test

มุมมอง 1.3Kปีที่แล้ว

00:00 Intro 00:17 Design behavior in waveform 00:48 Top level wrapper 01:04 Adding wires in top level 01:13 Instantiating design in top level 02:36 Driving stimulus to design - clock 03:20 Driving stimulus to design - reset 04:02 Driving stimulus to design - data 05:50 Monitoring output from design 08:11 Understanding test bench complexity

DRAM 03 - Memory Arrays

มุมมอง 1.7Kปีที่แล้ว

00:00 Introduction 00:14 Traditional addressing 01:20 Memory arrays 02:21 Row address and column address 03:05 Bank 04:20 Page 04:55 Writing operation 05:58 Reading operation

Writing SV UVM Testbench 01 - Design and Specification

มุมมอง 2.2Kปีที่แล้ว

Writing SV UVM Testbench 01 - Design and Specification

DRAM 01 - Introduction and Memory Cell Operation

มุมมอง 2.4Kปีที่แล้ว

DRAM 01 - Introduction and Memory Cell Operation

SystemVerilog Tutorial in 5 Minutes 19 - Compiler Directives

มุมมอง 3.8Kปีที่แล้ว

SystemVerilog Tutorial in 5 Minutes 19 - Compiler Directives

SystemVerilog Tutorial in 5 Minutes 18 - Cross Modules Reference

มุมมอง 5Kปีที่แล้ว

SystemVerilog Tutorial in 5 Minutes 18 - Cross Modules Reference

SystemVerilog Tutorial in 5 Minutes - 17a Concurrent Assertions

มุมมอง 6K2 ปีที่แล้ว

SystemVerilog Tutorial in 5 Minutes - 17a Concurrent Assertions

SystemVerilog Tutorial in 5 Minutes - 17 Assertion and Property

มุมมอง 14K2 ปีที่แล้ว

SystemVerilog Tutorial in 5 Minutes - 17 Assertion and Property

SystemVerilog Tutorial in 5 Minutes - 16 Program & Scheduling Semantics

มุมมอง 8K2 ปีที่แล้ว

SystemVerilog Tutorial in 5 Minutes - 16 Program & Scheduling Semantics

SystemVerilog Tutorial in 5 Minutes - 15 virtual interface

มุมมอง 6K2 ปีที่แล้ว

SystemVerilog Tutorial in 5 Minutes - 15 virtual interface

SystemVerilog Tutorial in 5 Minutes - 14 interface

มุมมอง 7K2 ปีที่แล้ว

SystemVerilog Tutorial in 5 Minutes - 14 interface

SystemVerilog Tutorial in 5 Minutes - 13a coverpoint bins

มุมมอง 6K2 ปีที่แล้ว

SystemVerilog Tutorial in 5 Minutes - 13a coverpoint bins

SystemVerilog Tutorial in 5 Minutes - 13 covergroup and coverpoint

มุมมอง 9K2 ปีที่แล้ว

SystemVerilog Tutorial in 5 Minutes - 13 covergroup and coverpoint

SystemVerilog Tutorial in 5 Minutes - 12e Class Polymorphism

มุมมอง 5K2 ปีที่แล้ว

SystemVerilog Tutorial in 5 Minutes - 12e Class Polymorphism

SystemVerilog Tutorial in 5 Minutes - 12d Class Inheritance

มุมมอง 4.4K2 ปีที่แล้ว

SystemVerilog Tutorial in 5 Minutes - 12d Class Inheritance

Great series. Please keep on adding more videos. Thanks!

Thanks for the comment. I'll try my best.

Thank you for such a informative video in short duration.

Glad you find it helpful 😊. Thanks for the comment too

Very well explained LKK 👍🏻😀

Glad you found it helpful!😊

Why music in background 😞😞

Thank you so much for mading these videos. These are very helpful and easy to understand.

Wow. Thanks a lot for your super thanks. Gotta say that's my first.

great❤

Thanks ❤️

Absolutely great video (Not just this one, I've seen more of your tutorial) but please next time lower the music volume it is very frustrating I just continue to follow it because it is very well done per the explanation and quality

Thanks. I've lowered the background music in later videos. Sorry bout that.

Very helpful, now I have only one video remaining. I am going to watch it tomorrow, once again thanks for your series.

Thanks. Glad it has been helpful🙂

Nice explanation❤. Wether same concept used in the lpddr memory or it differs? In terms of channel ,rank,bank,etc.....

Thanks. It's the same concept for lpddr as well.

So if I use 16gb dual rank in channel 1 (slot A2) + 8gb (slot A3) and 8gb (slot A4) in channel 2 (both single rank), will it run the same (or almost) as 16gb + 16gb in dual channel? I'm using that configuration.

I haven't studied it like that in a system level. Assuming the system can support it, the difference between the two would be the access timing, which is handled during training. I can't tell any performance difference, but like I said, I've never studied from the system level.

too much of background music is disturbing the original voice over.

You creating another channel after using me all these years shows the cruel nature of man 😢

I don't know who you are. And this channel is my own effort.

@@openlogic925 It is enough to say you don't know me after using me and blocking me on discord. Keep it up. Your fall is imminent

@@thesunwillshine11 Funnily enough, I don't know what discord means and have to search it up. Assuming you meant the social app discord, I have never used it. Once again, you got the wrong guy.

@@openlogic925 I got the wrong guy? Okay nah

The one video that explains the difference between using a module test and class test.

Hope it's a good thing 😊. Thanks

Done watching your systemverilog series. Thanks😊

Thanks. Hope it has been helpful. 😊

Love the way you made it easy to understand, we need more videos like this, please explain timing parameter, drift and ck to wck sync with write and read operation. Also, a separate video on command gap.

Thanks for the comment. These videos will come, but they'll take time.

This guy basically designed his own type of SRAM .SRAM uses OR gates and AND gates to store data it's called a gated latch

Yeah this guy is wrong that not how a not gate circuit looks like it only needs 1 transistor

I hope u make more contents about uvm. Wish your channel approach more people

Thanks. I have second thoughts on how the UVM videos will go. That's why I'm pausing on it for the moment.

can we use super keyword directly in the testbench to call parent class function ?

I assume you meant: object.super.func(). I've never tried that, based on my intuition, it's not allowed.

Interesting Video. I find it very helpful. I was wondering if you could do a video on black box verification. It's a fascinating topic and I'm curious to learn more about the how professional go about it and challenges in it. Thanks for your great work!"

Thanks for the comment and the duggestion. I have plans for this series but I'm currently busy with my day job. It'll be awhile before I can create such content. Thanks again.

I havent seen like this . This is damn cool

Glad it provides another perspective😊

Hello thx for lectures. In book i read that you dont need to add modports both module ports and top module (module instance) . you can just add in module ports or just add modport in top modules module instances ( i think second is better bcs it give you chance to reuse module with other modport) .

Thanks for comment and thanks for the pointer 😊

Awesome! I wish I had found it earlier!

Glad you find it helpful. It is still a long way before I can finish this series.

What will happen in the "foreach" example should the array be larger than 2'b?

So happens your questions has two meaning; if you mean the size b[1:0] changes to b[n-1:0], then foreach loop will loop n times instead of 2 times. If you mean the type bit changes to bit[n-1:0], then in this case, it will behave the same where it loops twice.

in the first example, base class has no constraints, when we point derived class object with base class handle and then we randomize. since base class handle does not have constraint "cst" why does it randomize with object's constraints ?

You ask why? That's the intent. If you ask how, I don't know for sure, but every class has inherited randomize function. Let's pretend randomize() comes from the base class, if that helps you to visualise it better. As a pointer, it just points to an object and call its randomize. Every object randomize function would locate its object rand variables and constraints and behave accordingly.

@@openlogic925 Thank you !!

Clear explanation! Thank you!

You're welcome. Thank you too

The way you explain the concepts in the easy way is wonderfull, Your explanation skills are fentastic sir.. Thank you from Raghavendra , India.

Glad it helps. Thanks for the comment 😊

waveforms are allmost incorrect - clk edge

I'm sorry I don't get it. If you don't mind enlightening me, which part exactly? Clk against cs/ca? I did think about aligning the clk edge to the middle cycle of cs/ca, but then I thought it's not important yet, until I create another video to look deeper. There are other aspects that I chose to "ignore" too for the time being, like the preamble behaviour. But then again, I'm not sure which part you're referring to.

Thank you, short and comprehensive explanation

You're welcome. And thanks for the comment😊

Great!

Thanks 😊

hi, could you explain the meaning of 'automatic' keyword in "module automatic test();". please? Many thanks.

I assume u know automatic with function and task? Putting automatic at module is the same as putting automatic for all the functions/tasks in the module.

BEST VIDEOS ABOUT SYSTEMVERILOG!!!!!!!!!!! Do you want to make PDF-book using this material?

Thanks for the kind comment. I thought about it, but didn't make any move on it.

I think x4 means 4 bits could be accessed externally at a time within 1 array, not 4 arrays.

I wonder what gives you that idea. First of all I'm not involved in dram design, so it's true that I'm guessing and that I don't know for sure. But... if one address can access a data (x4) and it comes from a same array, that means the 4 bits in that array have the same column / row address; in that case, row / column address has lost its meaning. I can't think of a logical explanation for this. So... I'm guessing it's correct that the x4 data comes from 4 arrays.

@@openlogic925 I think I know where the disconnect is. You were using a model to demonstrate the x4 concept whereas I was referring to an actual implementation.

@@openlogic925 I'd also like to add that a page is simply a row. So this also explains why in actual implementations, a bank is 1 big array (instead of viewing a bank as multiple stacked arrays, treat it as as 1 big 2-D array).

Hahaha... That's funnily embarrassing for me 😄. Just when I take a little pride in creating easy-to-understand visual, along came an expert saying I've been telling it wrong . I hope the only mistake is the stacking visual. It should be one array segregated to 4 regions, resembling 4 arrays. Thanks for the info. Though it does shaken me a little, about making guesses in future videos.

@@openlogic925 Hey brother, I am by no means an expert. I merely came across different DDR lectures online and noticed you explained some stuff differently. The model you used to demonstrate the x4 (wide column-width) concept is great for visualizing what's going on under the hood. I appreciate your high quality videos.

Thank you for making these videos, you are doing a great job! I don't think you need to worry about the way you speak English. We can understand you 100%!

Thanks 😀. I'm sure there is a huge room for improvement.

the background music makes it difficult to hear what you teaching

Series worth binge watching and to feel amazed about so much of learning bombardments after its completion And then to watch individual vidoes so to digest down while handson practicing every topics one by one ThankYou

I fe like I've just won academy awards for best animated series 😁. Thanks for the kind comment. I apologise in advanced, soon you'll see some mistakes in the code. I haven't had the time to compile them into description yet. Sorry bout that.

I have never seen a more clear explanation....Thank you very much

Glad it was helpful!

Thank you, clear and precise.

Thanks. Glad it helps

Background music doesn't require kindly remove if possible.

Depends on what is impossible. It's posiisble to reupload new videos replacing the old ones, though it's impossible to remove the music in existing videos. I'm gym thinking to replace, but not quite yet.

I have walked through

Hope it helped 😊

I have walked through this video it is informative and easy to understand

Thanks. Glad it helped

I have walked through this video. it is informative and easy to understand. Nice keep it up.

Thanks. I'll try 😊

Awesome explanation !!

Thanks for the comment 😃

I am impressed how you explain the theory so understandable, thanks for your contribution. Can I ask about name of the tool you used in 6:23 to plot the waveform?

Thanks. I'm just using PowerPoint in this presentation.

Open Logic for president! Best System Verilog introduction anywhere in the Interwebs.

Haha. I'm sure the presidential campaign would be fun. Thanks 😊

Love this video. It's very helpful

Thanks. Glad it helps 🙂

Good video

Thanks.

These are great videos. I learned a lot about DRR memory. Great illustrations. To help make these better, I'd suggest replacing "in simplicity" with something like "in short" or "in essence" or "essentially", something like that.

Thanks. But very interesting suggestion; I mean I'm not sure why that particular one, if you don't mind, do entertain me. Overall I'm aware of the slang that I have. But the videos probably would never happen if I were to improve my English to a native speaker level. Of course nowadays I probably can use a generative AI voice. Thanks again.

@@openlogic925 Please, no AI. Keep it as it is. It's the only one that keeps recurring that's a bit strange. All other "imperfection" are quite understandable for a non native speaker.

@@mdesm2005 Thanks for the response. I'll pay attention in the future

Thank you for the clear explanation!

You're welcome. Glad it helps 🙂

OMGoodness! This video is easy to follow with great visual aid. Please keep it coming. You have a new subscriber.

Thanks for the comment. I'm currently busy with my job. I'll post new materials as soon as possible.